UNIVERSITY OF COPENHAGEN FACULTY OF SCIENCE NIELS BOHR INSTITUTE

## Development of superconducting gatemon qubits based on selective-area-grown semiconductors

Albert Hertel

Ph.D. Thesis Center for Quantum Devices Niels Bohr Institute University of Copenhagen

Academic advisor: Prof. Charles M. Marcus Assessment committee: Assoc. Prof. Kasper Grove-Rasmussen Assoc. Prof. William D. Oliver Asst. Prof. Javad Shabani

February 2021

Center for Quantum Devices

### Abstract

Currently much experimental effort at universities and companies focuses on the development of large scale quantum computers. Quantum computers are believed to enable solving certain computational problems faster than classical computers, thus revolutionizing many fields in science. Many different technologies are competing to overcome challenges in scaling today's small quantum processors to practically useful fault tolerant quantum computers. Superconducting qubits – in particular transmon-type qubits – are a leading technology in the field and the subgroup of gate-tunable transmons has recently shown strong potential to become a platform for low crosstalk and low dissipation qubit systems.

This thesis presents novel material platforms for scalable voltage-controlled semiconductor-based superconducting transmon qubits (gatemons). These gatemons are based on selective-area-grown InAs/Al hybrid structures which are monolithically integrated into a high resistivity silicon substrate (Si SAG) or InP substrate (InP SAG).

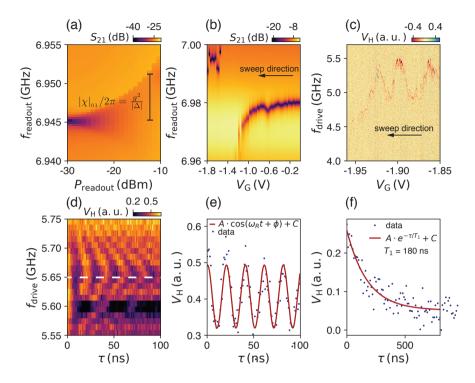

Starting with proof-of-principle demonstrations, the InP SAG material system is introduced and the gatemon fabrication is outlined. Coherent oscillations are demonstrated and coherence times  $T_1 \approx 180$  ns and  $T_2^* \approx 10$  ns are measured. To improve coherence times, an alternative growth sequence is explored and the electric properties of the material are characterized.

Moving towards gatemons on silicon, the electrical properties of Si SAG at millikelvin temperatures are characterized where we observe a high average field-effect mobility of  $\mu \approx 3200 \text{ cm}^2/\text{Vs}$  for the InAs channel, a hard induced superconducting gap, high transparency Josephson junctions  $\mathcal{T} \approx 0.75$  and signatures of multiple Andreev reflections. Josephson junctions exhibit a gate voltage tunable switching current with  $I_C R_N \approx 83 \,\mu\text{V}$ .

Finally, we discuss the RF properties of Si SAG and demonstrate that high quality resonators can be fabricated on the silicon substrate. After detailing the gatemon device fabrication, we describe the measurement of coherent oscillations and coherence times  $T_1 \approx 380$  ns and  $T_2^* \approx 15$  ns are measured. Possible steps towards increased coherence times are outlined.

In summary, the work presented in this thesis presents a novel and promising material platform for scalable voltage-controlled qubit circuitry.

## Acknowledgments

The past three years have been a very special time for me and would not have been the same if it was not for the many people who make QDev a unique place.

I want to express my gratitude to my supervisor **Charlie** for giving me the opportunity to work in this interesting field, for always having useful feedback, caring about the education of his students, trying to cheer me up with anecdotes and asking "what's next?".

I would like to thank **Karl** for leading the project and always being helpful when discussing the big picture and small experimental details.

I would like to thank the assessment committee members **Kasper Grove-Rasmussen**, **Will Oliver** and **Javad Shabani** for taking the time to evaluate this thesis.

Next, I want to thank all current and former group members of the always changing gatemon/transmon team for fruitful group meetings and valuable discussions: Natalie, Anders, Vivek, Michaela, Sachin, Pasquale, Lucas, Thorvald, Rob, Anna, Sangeeth, Smitha, Morten, José, Oscar, David, Malcolm, Ahnaf, Billy, Laurits, Carlo and Lillian. Thank you Michaela for believing in Si SAG, keeping your head up when things did not work as planned and keeping up with my supervision when I was busy.

A big thanks goes to our collaborators at Purdue University, **Mike**, **Geoff** and **Sergei**, for growing great material and the great collaboration during the past years. Further, I want to thank **Lucia** and **Valentina** from NEST and the **Krogstrup group** for their collaboration and great materials.

I would give a special thanks to **Natalie** who has been a great help and very often a voice of reason in all my time in QDev. You were the best office neighbor and academic co-parent I could have hoped for. I also want to thank the shared second best office buddy, **Anders**, for always discussing life in general and physics with me, for having useful comments, especially towards the end of our time at QDev. Thank you to the other shared second best office buddy **Lukas** for all the interesting chats we had, disc golf competitions, an honorable participation in the two minor meme disputes and creating fresh memes.

My special thanks goes to **Fabio** for all the coffee breaks, listening to complaints, dishing out complaints, always including everyone in after hour activities and trying to redirect the group to Rudo at the end of every single evening. Thank you to **Damon** for sharing your scientific wisdom, deep thoughts and trying to make the science world a better place.

I am very thankful to **Shiv** and **Rob** for helping me to get started in the cleanroom and always being enthusiastic about new fab challenges.

Thank you to **Alisa** and **John** for opening a pub that looks very much like a living room, as well as **Karolis** and **Dags** for being regular guests and bringing all the good jokes and good atmosphere that a real pub needs.

One of QDev's biggest strengths is that it is a melting pot where many different people meet and enjoy their time together. I want to thank Abhishek, Alexander, Anasua, Andreas, Asbjørn, Denise, DJ Antonio, Eoin, Esteban, Federico, Filip K., Filip M., Gerbold, Judith, Maren, Sole for all the wonderful moments.

I want to thank the people who proof-read this thesis and gave great feedback: Anders, Damon, Natalie, Fabio, Michaela, Anasua, Karolis and Alisa. Thank you for constructive and sometimes humorous comments.

My very special thanks goes to Heidelberg Instruments, who, in the time of great need, were always trying to make things work.

I want to thank my fridge **T2** for possibly being the best fridge in the world, for enduring multiple upgrades and repairs, as well as always staying cool. I also want to thank **T5**, a.k.a. Kevin, for possibly being the most difficult and unfaithful fridge in the world, but for showing me that one can make most things work by trying hard and not giving up.

A special thanks goes to all the people at QDev, who often work in the background and make sure that things run smoothly. I want to thank the administrative team **Dorthe**, **Maria**, **Katrin**, **Trine**, **Monica**, **Tina** and **Marianne**, who are always willing to help and organize great events. Thank you to the E-shop team **Ruben**, **Rikke** and **Rasmus** for always being helpful and sharing their expertise. Further, I want to thank **Jan**, **Morten** and **Lars** from the mechanical workshop, who always made great fridge equipment for us. I also want to thank the cleanroom team, **Claus**, **Karolis**, **Nader**, **Martin**, who kept our great cleanroom running and were always helpful.

Finally, I want to thank the important people in my life who exist outside of

the world of physics. A big thank you to my friends from home **Jonas**, **Kilian**, **Mathias** and **Arne**, who demonstrate every day that the most fascinating stories take place in and around Hagen and not Copenhagen. Further, I want to thank my big family for supporting me during my studies and throughout my PhD. The biggest thank you of all goes to **Lisa**, who is simply the best, who made every great day even greater and turned every bad day into an okayish day.

## Contents

| 1 | Intr                            | oduction                                   | 17 |  |

|---|---------------------------------|--------------------------------------------|----|--|

|   | 1.1                             | Thesis outline                             | 19 |  |

| 2 | Circuit Quantum Electrodynamics |                                            |    |  |

|   | 2.1                             | Quantized LC oscillator                    | 22 |  |

|   | 2.2                             | Anharmonic quantum oscillator              | 26 |  |

|   | 2.3                             | Transmon                                   | 29 |  |

|   | 2.4                             | Qubit readout                              | 34 |  |

|   | 2.5                             | Qubit manipulation                         | 37 |  |

|   | 2.6                             | Semiconductor-based superconducting qubits | 38 |  |

| 3 | Sup                             | erconductor-Semiconductor Hybrid Systems   | 43 |  |

|   | 3.1                             | Andreev reflections                        | 43 |  |

|   | 3.2                             | Transport across NS interface              | 45 |  |

|   | 3.3                             | SNS junction                               | 50 |  |

|   | 3.4                             | RCSJ model                                 | 52 |  |

|   | 3.5                             | Short vs. long junction                    | 55 |  |

|   | 3.6                             | Finite-voltage regime of an SNS junction   | 56 |  |

| 4 | Exp                             | erimental Methods                          | 59 |  |

|   | 4.1                             | cQED requirements for material systems     | 59 |  |

|   | 4.2                             | Selective area growth technique            | 62 |  |

|   | 4.3                             | Device layout                              | 62 |  |

|   | 4.4                             | Mounting the devices                       | 65 |  |

|   | 4.5                             | Dilution refrigerator                      | 67 |  |

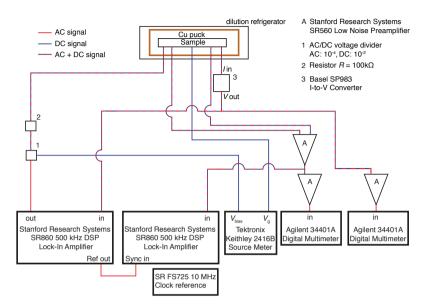

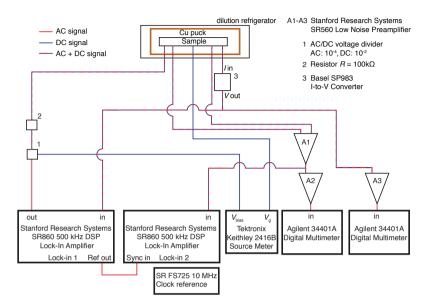

|   | 4.6                             | DC transport setup                         | 71 |  |

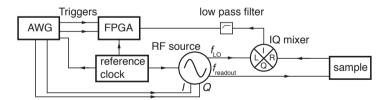

|   | 4.7                             | cQED measurement techniques                | 73 |  |

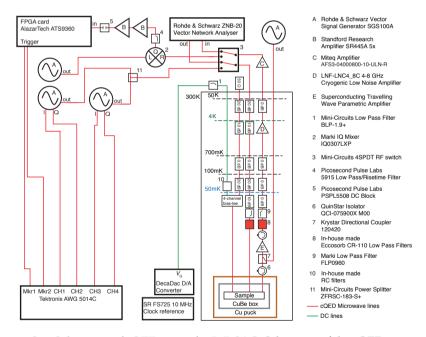

|   | 4.8                             | cQED setup                                 | 78 |  |

| 5 | The                             | InP SAGmon                                 | 81 |  |

|   | 5.1                             | First generation devices                   | 81 |  |

|   | 5.2                             | Second generation devices                  | 91 |  |

| 6  | Elec                                                                          | trical Properties of Si SAG                              | 99                                                                                                                                                               |

|----|-------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 6.1                                                                           | Material growth                                          | . 100                                                                                                                                                            |

|    | 6.2                                                                           | Devices                                                  | . 102                                                                                                                                                            |

|    | 6.3                                                                           | Field-effect measurements                                | . 103                                                                                                                                                            |

|    | 6.4                                                                           | Induced superconducting gap                              | . 105                                                                                                                                                            |

|    | 6.5                                                                           | Nanowire Josephson junctions                             |                                                                                                                                                                  |

|    | 6.6                                                                           | Multiple Andreev reflections                             |                                                                                                                                                                  |

|    | 6.7                                                                           | Discussion and Conclusions                               |                                                                                                                                                                  |

| 7  | The                                                                           | Si SAGmon                                                | 113                                                                                                                                                              |

|    | 7.1                                                                           | RF material properties                                   | . 113                                                                                                                                                            |

|    | 7.2                                                                           | Device fabrication                                       | . 117                                                                                                                                                            |

|    | 7.3                                                                           | Qubit devices                                            | . 119                                                                                                                                                            |

|    | 7.4                                                                           | Discussion and Outlook                                   | . 127                                                                                                                                                            |

| 8  | Con                                                                           | clusion and Outlook                                      | 129                                                                                                                                                              |

|    | 8.1                                                                           | Summary                                                  | . 129                                                                                                                                                            |

|    | 8.2                                                                           | Outlook                                                  | . 130                                                                                                                                                            |

|    |                                                                               |                                                          |                                                                                                                                                                  |

| Aj | opend                                                                         | dix A Material Growth InP SAGmon                         | 133                                                                                                                                                              |

| A  | -                                                                             | dix A Material Growth InP SAGmon Growth mask preparation |                                                                                                                                                                  |

| A  | A.1                                                                           |                                                          | . 134                                                                                                                                                            |

| A  | A.1<br>A.2                                                                    | Growth mask preparation                                  | . 134<br>. 135                                                                                                                                                   |

| -  | A.1<br>A.2<br>A.3                                                             | Growth mask preparation                                  | . 134<br>. 135                                                                                                                                                   |

| -  | A.1<br>A.2<br>A.3                                                             | Growth mask preparation                                  | <ul> <li>. 134</li> <li>. 135</li> <li>. 135</li> <li>. 137</li> </ul>                                                                                           |

| -  | A.1<br>A.2<br>A.3                                                             | Growth mask preparation                                  | <ul> <li>. 134</li> <li>. 135</li> <li>. 135</li> <li>. 137</li> <li>. 137</li> </ul>                                                                            |

| -  | A.1<br>A.2<br>A.3<br><b>ppend</b><br>B.1                                      | Growth mask preparation                                  | <ul> <li>134</li> <li>135</li> <li>135</li> <li>137</li> <li>137</li> <li>140</li> </ul>                                                                         |

| -  | A.1<br>A.2<br>A.3<br><b>ppend</b><br>B.1<br>B.2                               | Growth mask preparation                                  | <ul> <li>. 134</li> <li>. 135</li> <li>. 135</li> <li>. 137</li> <li>. 137</li> <li>. 140</li> <li>. 146</li> </ul>                                              |

| Aj | A.1<br>A.2<br>A.3<br><b>opend</b><br>B.1<br>B.2<br>B.3<br>B.4                 | Growth mask preparation                                  | <ul> <li>. 134</li> <li>. 135</li> <li>. 135</li> <li>. 137</li> <li>. 137</li> <li>. 140</li> <li>. 146</li> <li>. 148</li> </ul>                               |

| Aµ | A.1<br>A.2<br>A.3<br><b>ppend</b><br>B.1<br>B.2<br>B.3<br>B.4<br><b>ppend</b> | Growth mask preparation                                  | <ul> <li>. 134</li> <li>. 135</li> <li>. 135</li> <li>. 137</li> <li>. 137</li> <li>. 140</li> <li>. 146</li> </ul>                                              |

| Aµ | A.1<br>A.2<br>A.3<br><b>ppend</b><br>B.1<br>B.2<br>B.3<br>B.4<br><b>ppend</b> | Growth mask preparation                                  | <ul> <li>. 134</li> <li>. 135</li> <li>. 135</li> <li>. 137</li> <li>. 137</li> <li>. 140</li> <li>. 146</li> <li>. 148</li> <li>. 151</li> <li>. 155</li> </ul> |

| Aµ | A.1<br>A.2<br>A.3<br>Deno<br>B.1<br>B.2<br>B.3<br>B.4<br>Deno<br>D.1          | Growth mask preparation                                  | <ul> <li>134</li> <li>135</li> <li>137</li> <li>137</li> <li>137</li> <li>140</li> <li>146</li> <li>148</li> <li>151</li> <li>155</li> </ul>                     |

| Append     | lix F Si SAG transport supplementary material                                  | 161 |

|------------|--------------------------------------------------------------------------------|-----|

| F.1        | Material and device fabrication                                                | 161 |

| F.2        | Coherence Length Estimate                                                      | 162 |

| F.3        | Tunneling spectroscopy                                                         | 163 |

| G.1        | dix G Si SAG devices         Mask preparation         Qubit device fabrication |     |

| References |                                                                                |     |

## List of Publications

The work of this thesis has resulted in the following publications:

1. Albert Hertel, Laurits O. Andersen, David M. T. van Zanten, Michaela Eichinger, Pasquale Scarlino, Sachin Yadav, Karthik Jambunathan, Sergei Gronin, Geoff C. Gardner, Michael J. Manfra, C. M. Marcus, Karl D. Petersson

Electrical Properties of Selective-Area-Grown Superconductor-Semiconductor Hybrid Structures on Silicon

*Manuscript in preparation for submission to Physical Review Applied, in large parts identical to Chapter 6..*

#### 2. Albert Hertel et al.

Manuscript in preparation based on the results in Chapter 7. Planning submission to Physical Review Applied.

## List of Figures

| 2.1  | Quantum <i>LC</i> oscillator circuit and potential          | 22 |

|------|-------------------------------------------------------------|----|

| 2.2  | Coplanar waveguide geometry                                 | 25 |

| 2.3  | Quantum anharmonic oscillator circuit and potential         | 27 |

| 2.4  | Cooper pair box circuit                                     | 30 |

| 2.5  | Numerical solutions to transmon Hamiltonian                 | 31 |

| 2.6  | Coupled transmon circuit.                                   | 34 |

| 2.7  | Bloch sphere                                                | 38 |

| 2.8  | Short junction potential                                    | 39 |

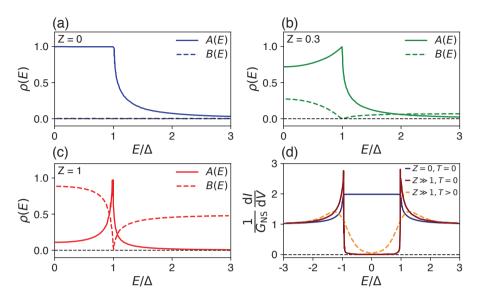

| 3.1  | Andreev reflections in real and energy space                | 44 |

| 3.2  | Schematic NS interface in the BTK model                     | 45 |

| 3.3  | BTK model solutions                                         | 48 |

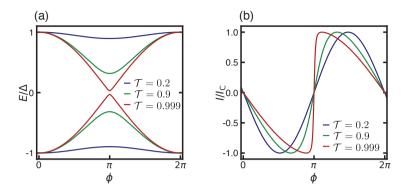

| 3.4  | Andreev bound state energies                                | 51 |

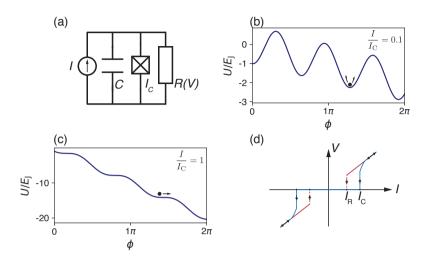

| 3.5  | RCSJ model                                                  | 53 |

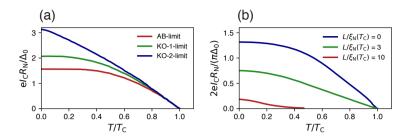

| 3.6  | $I_{\rm C}R_{\rm N}$ product temperature dependence         | 56 |

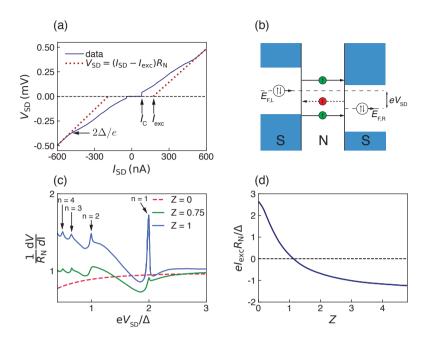

| 3.7  | OBTK model predictions                                      | 57 |

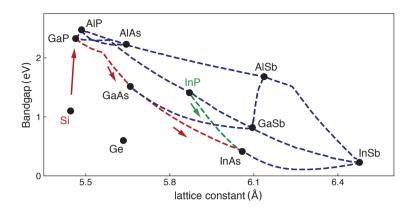

| 4.1  | Lattice constant vs. bandgap diagram of commonly used semi- |    |

|      | conductors                                                  | 61 |

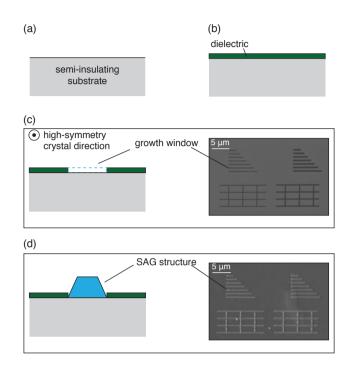

| 4.2  | Schematic of selective area growth principle                | 63 |

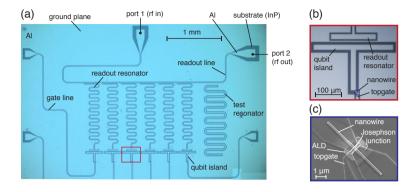

| 4.3  | Qubit device layout                                         | 64 |

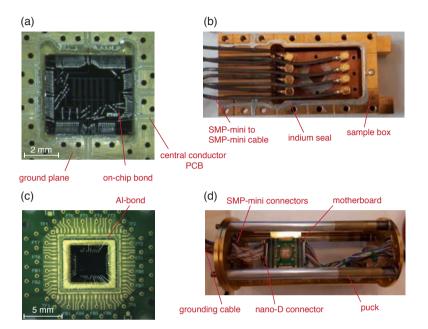

| 4.4  | Device Packaging                                            | 66 |

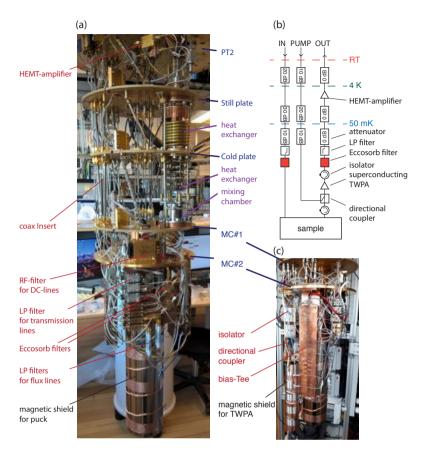

| 4.5  | Dilution refrigerator setup                                 | 69 |

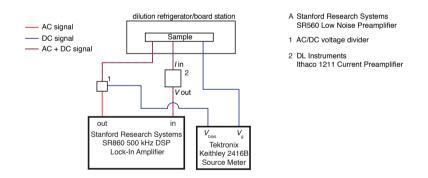

| 4.6  | Schematic of the DC measurement setup                       | 72 |

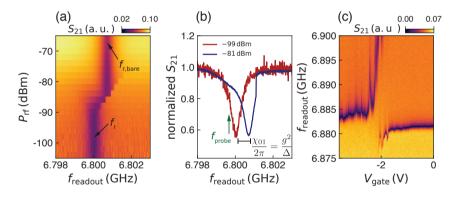

| 4.7  | Examples of continous readout measurements                  | 73 |

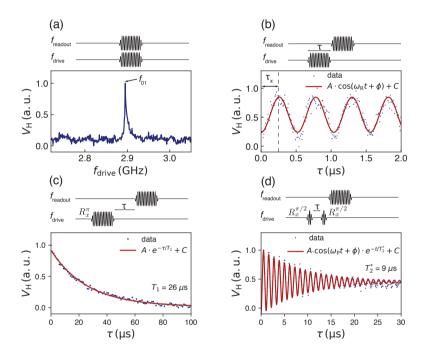

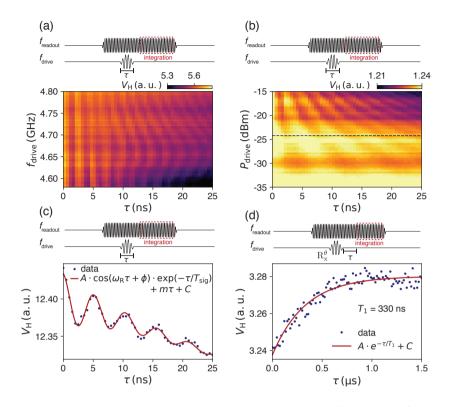

| 4.8  | Examples of pulsed readout measurements                     | 74 |

| 4.9  | Schematic of a demodulation circuit                         | 76 |

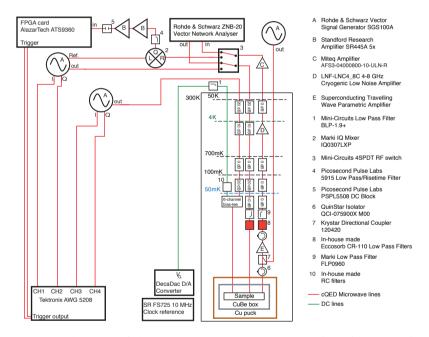

| 4.10 | Schematic of the cQED measurement setup                     | 78 |

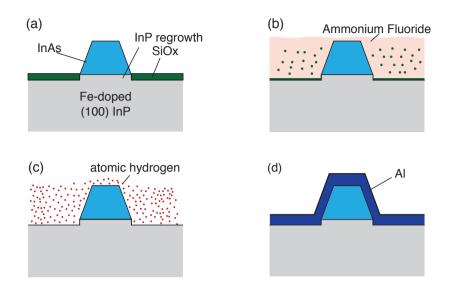

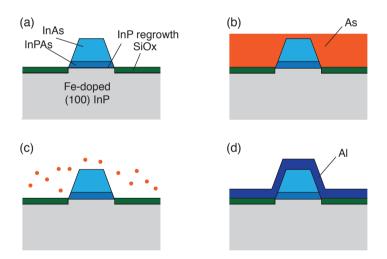

| 5.1  | First generation InP SAGmon growth sequence                 | 83 |

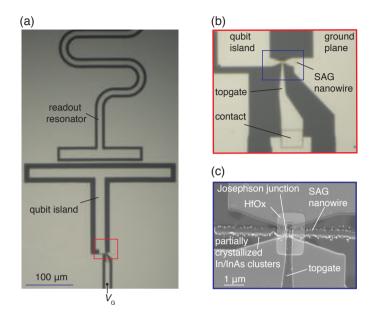

| 5.2  | First generation InP SAGmon devices                         | 84 |

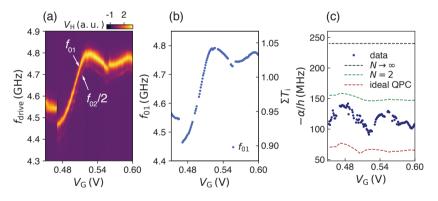

| 5.3  | InP SAGmon qubit measurements                               | 86 |

| 5.4 | InP SAGmon $T_2^*$ measurements                        |

|-----|--------------------------------------------------------|

| 5.5 | Anharmonicity analysis InP SAGmon                      |

| 5.6 | Second generation InP SAGmon growth sequence           |

| 5.7 | Second generation InP SAG DC transport                 |

| 5.8 | Second generation InP SAGmon devices                   |

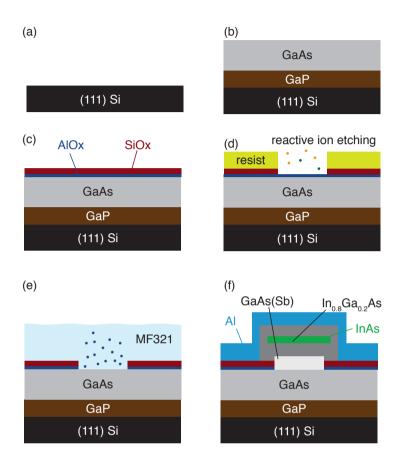

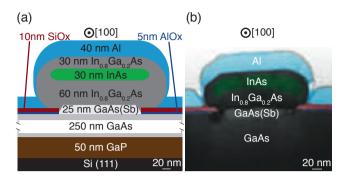

| 6.1 | Si SAG growth sequence                                 |

| 6.2 | Si SAG material stack                                  |

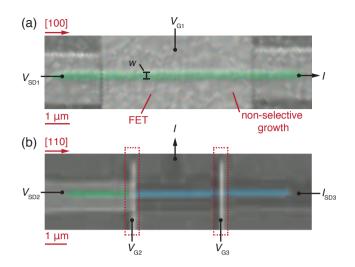

| 6.3 | Si SAG tranport devices                                |

| 6.4 | Si SAG FET data                                        |

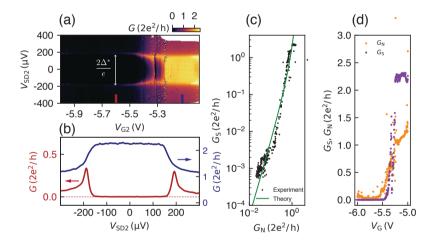

| 6.5 | Si SAG NIS spectroscopy data                           |

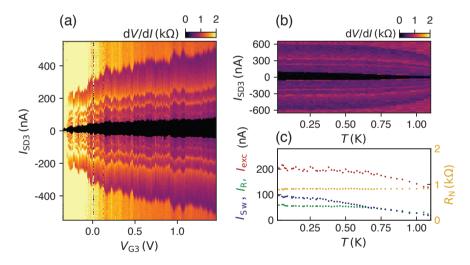

| 6.6 | Si SAG Josephson junction data 108                     |

| 6.7 | Si SAG multple Andreev reflection data                 |

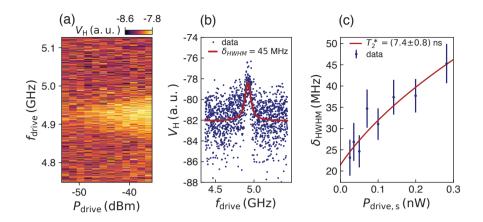

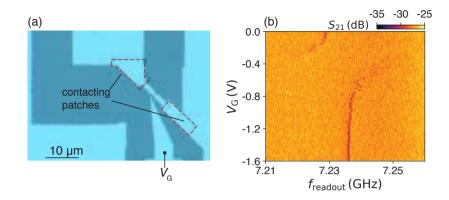

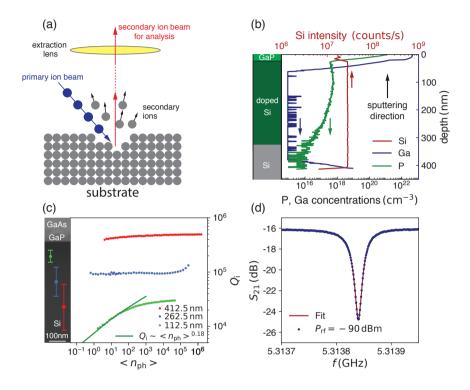

| 7.1 | RF properties of Si SAG material                       |

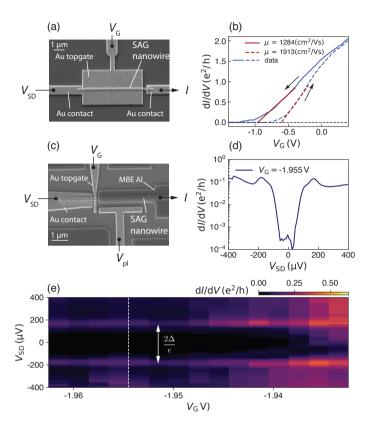

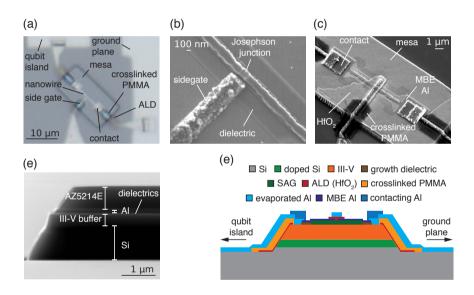

| 7.2 | Gatemon devices farbicated with Si SAG                 |

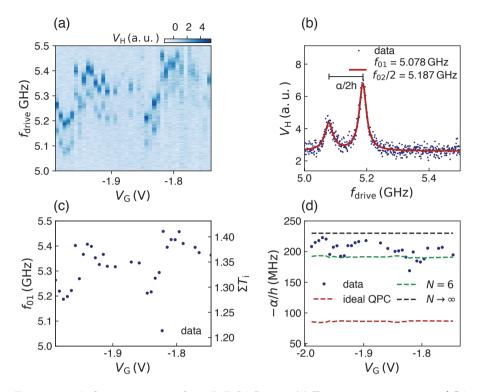

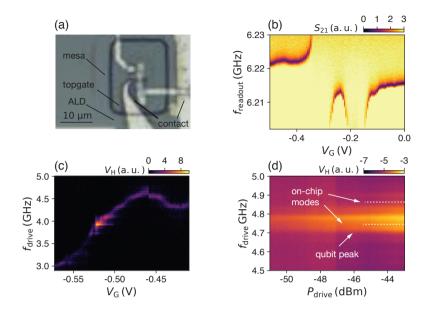

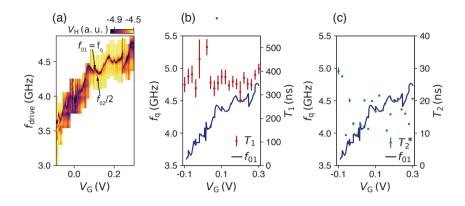

| 7.3 | Spectroscopy data for devices without PMMA bridges 120 |

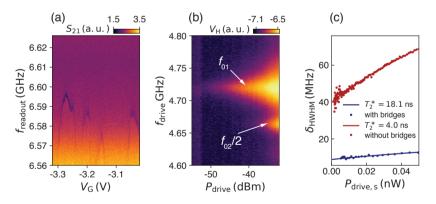

| 7.4 | Spectroscopy data for devices with PMMA bridges        |

| 7.5 | Anharmonicity of the Si SAGmon                         |

| 7.6 | Coherent oscillation Si SAGmon                         |

| 7.7 | Coherence times Si SAGmon                              |

| C.1 | Schematic of DC transport setup for InP SAG            |

| C.2 | Schematic of cQED setup for InP SAG 152                |

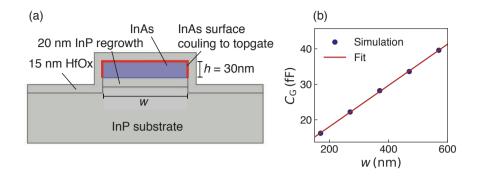

| D.1 | Gate capacitance simulation for InP SAG                |

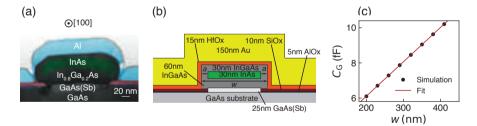

| D.2 | Gate capacitance simulation for Si SAG                 |

| E.1 | Schematic of DC measurement setup for Si SAG 158       |

| F.1 | Si SAG additional tunneling spectroscopy data          |

| F.2 | Si SAG additional Josephson junction data              |

# Introduction

Currently the world is eagerly awaiting the arrival of the first large scale quantum computer. Inspired by the possibility that quantum computers could revolutionize certain fields in science by solving specific computational problems significantly faster than classical computers [1–4], many research groups and companies are working towards the first quantum computer. The media is closely following the efforts and documenting major breakthroughs in the field, such as the recent demonstration of quantum speed up [5], commenting on how a concept once considered science-fiction slowly becomes reality.

The essential building block of a future quantum computer is the quantum bit (short: qubit), which is built from a quantum two-level system [6]. In contrast to the classical bit, a qubit can be in a superposition of the ground and excited state. A system with N qubits can therefore be prepared in  $2^N$  states, leading to an exponential growth of available states with each additional qubit [7]. Further, quantum states can be entangled, which can be harvested as computation speed up by parallelizing computations [7].

The challenges to building a real quantum computer are manifold. Focusing on the hardware aspect, highly coherent and controllable qubits are required. To readout the qubit states, qubits must inevitably be coupled to the environment and thus to noise sources, causing qubit decoherence. Tremendous progress has been made in the last decade to increase coherence times, reliably reaching coherence times above ~ 100 ms in superconducting qubits [8,9]. Adding to this challenge, even the simplest quantum algorithms require several qubits [4], meaning qubit-qubit interactions are an essential part of quantum computing. Interconnecting qubits creates parasitic crosstalk between qubits and is a potential source of decoherence. Due to the limited coherence and control of qubits, quantum error detection and correction is assumed to be a necessary ingredient for quantum computers [4,10,11]. Most suggested error corrections schemes, such as the surface code [12], utilize many physical qubits to build one logical qubit. Depending on the assumed error rates, it is estimated that  $10^5 - 10^6$  physical qubits will be needed for useful large scale quantum computers [13].

Scaling up to a large number of interconnected qubits sets challenges beyond the device level. Examples are (a) the relatively large footprint of most qubit systems in combination with the limited volume of dilution refrigerators, which are used to cool down many types of qubits to their operation temperature at millikelvin temperatures, and (b) that data acquisition and processing must be performed using classical computers. With these requirements in mind, several qubit platforms have been developed. Some of these are superconducting qubits [9, 14, 15], electrons confined in quantum dots [16–18] and trapped ions [19,20]. All platforms have their own advantages and disadvantages and compete to be the foundation for future qubit architectures. In parallel, much experimental effort is put into the development of alternative platforms that have the potential to alleviate the challenges of scaling up quantum computers. The work presented in this thesis is part of this experimental effort.

This thesis focuses on the development of a new scalable platform for superconducting qubits using semiconductor-superconductor hybrid systems. These qubits can be classified as gate-voltage controlled transmons, called "gatemons" [21,22]. A transmon uses a Josephson junction to create an anharmonic oscillator [23,24]. In the 'standard' transmon, the Josephson junction is almost exclusively made as an insulating tunnel junction, using aluminium oxide sandwiched between two aluminium electrodes. Transmons are usually controlled using magnetic flux generated at the device level by milliampere currents, which can lead to heating or crosstalk between qubits [22]. Due to the voltage tunability of the junction, the qubit frequency can be voltage controlled, removing the need for large currents and potentially reducing crosstalk. Although a promising new platform, gatemons [25,26] have not reached the high coherence times typically achieved with state-of-the-art transmons [9]. Additionally, current gatemon platforms have either poor scalability [21,27] or poor coherence times due to losses in the underlying III-V substrate [28]. In this work we develop a gatemon platform using selective area growth techniques that has the potential to overcome current limitations and combine scalability and high coherence.

#### 1.1 Thesis outline

This thesis reports the experimental efforts and progress in creating gatemons using selective-area-grown InAs/Al structures.

Chapter 2 introduces the basics of circuit quantum electrodynamics and discusses the implication of a semiconducting Josephson junction for a superconducting qubit, providing the necessary theoretical framework to understand the experimental data presented in Chapters 5 and 7.

Continuing the discussion about semiconductor-superconductor hybrid systems, Chapter 3 presents the theoretical framework for these systems in term of Andreev reflections. The chapter introduces the BTK theory, the SNS junction, the RCSJ model, the  $I_CR_N$  product and OBTK theory, which are necessary to understand the experiments presented in Chapter 6.

Chapter 4 presents our requirements for a platform for scalable and highly coherent gatemons. Further, it details the device fabrication, measurement setups and measurement techniques used in this work.

Chapter 5 introduces the InP SAG material system, outlines gatemon fabrication and presents proof-of-principle measurements showing that selectivearea-grown structures can be used to make gatemons. Possible sources of decoherence are discussed and the growth adjusted for it. Material with the adjusted growth is characterized in DC transport, where a sufficiently high field-effect mobility and hard induced superconducting gap is found, leading to the decision to continue with qubit fabrication. These devices showed a gate response but no coherent oscillation, which can be explained by short lifetimes.

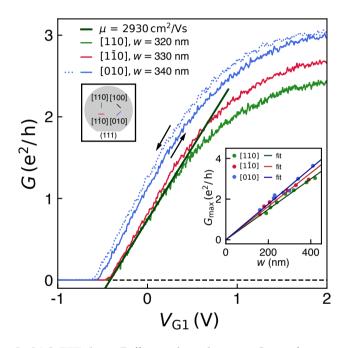

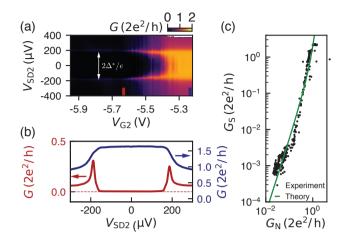

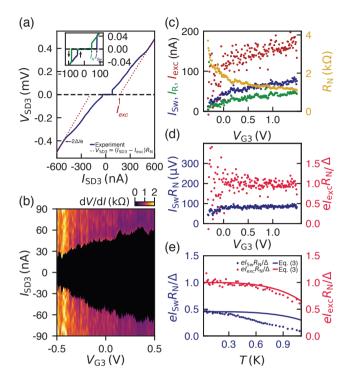

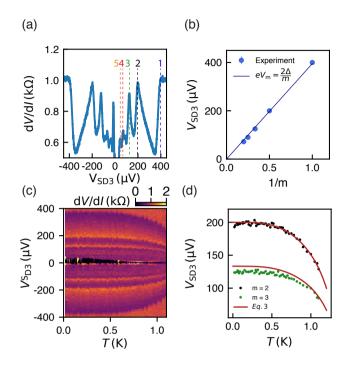

Chapter 6 introduces the Si SAG material system and characterizes its DC transport properties in terms of requirements for cQED applications. The measured properties are the field-effect mobility of the InAs channel, the induced

superconducting gap, the Josephson junction transparency and signatures of multiple Andreev reflections. Based on these results, we concluded that the material system is a suitable candidate for scalable gate voltage tunable transmon devices and other superconductor-semiconductor hybrid devices fabricated directly on Si.

Chapter 7 presents the RF properties of Si SAG and demonstrates that high quality (low loss) resonators can be fabricated on the Si substrate. This chapter details the device fabrication and presents coherent oscillations and measurements of the coherence times times in these devices. Further, the junction characteristics are probed using the qubit anharmonicity measurements. The chapter concludes with an outline of possible modifications to the device fabrication to improve the device performance.

Chapter 8 summarizes the results of this thesis and gives an outlook on possible future experiments using the Si SAG platform that would benefit and advance the field.

## 2

## **Circuit Quantum Electrodynamics**

Circuit quantum electrodynamics (circuit QED, or in short cQED) describes the light-matter interaction of a quantum system interacting with microwave photons [15, 24]. In particular, cQED describes superconducting systems as artificial atoms coupled to photons. Based on this successful theoretical framework, superconducting qubits have played a key role in quantum information experiments and the exploration of fundamental laws of quantum mechanics [9,24]. In this work, only a brief overview of basic concepts of cQED will be given. Understanding cQED is fundamental to superconducting qubits and provides the building blocks for qubits with novel material systems such as the systems presented in this thesis. These concepts are crucial for understanding the measurements presented in Chapters 5 and 7. Section 2.1 introduces the concept of the quantum LC oscillator. Hereafter, the anharmonic quantum oscillator and transmon qubit are described in Sections 2.2 and 2.3. This is followed by the discussion of qubit readout and manipulation in the framework of the Jaynes-Cummings model in Sections 2.4 and 2.5. The final section of this chapter discusses the implication of building a superconducting qubit with a semiconductor-based Josephson junction.

#### 2.1 QUANTIZED LC OSCILLATOR

One of the simplest quantum circuits that can be experimentally realized is the LC oscillator, which consists of an inductor with inductance L, and capacitor, with capacitance C. The corresponding circuit diagram is shown in Fig. 2.1(a). This circuit does not contain any resistors or dissipative elements and is therefore undamped. This is a good approximation to experimental superconducting circuits as the current flow in a superconductor is dissipationless [29]. This can be explained as a consequence of the superconducting gap  $2\Delta$  [30] that originates from electrons with opposite spin pairing up to form Cooper pairs [31]. These Cooper pairs condense into a resistance-free ground state, where  $2\Delta$  is the energy needed to break a Cooper pair and create single particle excitations. This means that single-particle excitations are effectively suppressed as they require the breaking of a Cooper pair, which is energetically expensive. Collective excitations are lifted to optical frequencies by the long-range Coulomb interaction [24]. Optical frequencies are several orders of magnitude higher than the eigenfrequencies of the LC circuit. Choosing the capacitance charge q as coordinate, the Lagrangian  $\mathcal{L}$  of the LC oscillator can be written in terms of a single degree of freedom as follows:

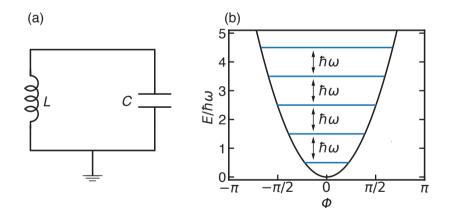

**Figure 2.1:** Quantum *LC* oscillator circuit and potential. (a) Circuit diagram of an oscillator with an inductance *L* and a capacitance *C* in parallel. (b) Harmonic potential of the quantum *LC* oscillator with energy levels  $E = \hbar \omega (\frac{1}{2} + n)$ , where  $n \ge 0$ .

$$\mathcal{L} = \frac{L}{2}\dot{q}^2 - \frac{q^2}{2C}.$$

(2.1)

The time derivative of the charge,  $\dot{q} = I$ , is the current through the capacitor. The flux through the inductor,  $\Phi$ , can be expressed as the momentum conjugate to the charge by

$$\frac{\partial \mathcal{L}}{\partial \dot{q}} = L\dot{q} = LI = \Phi.$$

(2.2)

Using the equations above, the Hamiltonian can be written as

$$H = \Phi \dot{q} - \mathcal{L} = \frac{\Phi^2}{2L} + \frac{q^2}{2C}.$$

(2.3)

This Hamiltonian corresponds to a classical harmonic oscillator with mass *L*, a spring constant 1/C and a resonance frequency  $\omega = 1/\sqrt{LC}$ . In order to treat the system quantum mechanically the coordinate and conjugate momentum can be promoted to quantum operators  $\hat{q}$  and  $\hat{\Phi}$ . By definition these fulfill the canonical commutation relation

$$\left[\hat{q}, \hat{\Phi}\right] = i\hbar. \tag{2.4}$$

This allows us to rewrite the Hamiltonian as

$$\hat{H} = \hbar\omega \left( \hat{a}^{\dagger} \hat{a} + \frac{1}{2} \right) \tag{2.5}$$

in terms of the raising and lowering operators

$$\hat{a}^{\dagger} = \frac{1}{\sqrt{2\hbar\omega C}}\hat{q} + i\frac{1}{\sqrt{2\hbar\omega L}}\hat{\Phi}$$

(2.6)

$$\hat{a} = \frac{1}{\sqrt{2\hbar\omega C}}\hat{q} - i\frac{1}{\sqrt{2\hbar\omega L}}\hat{\Phi},$$

(2.7)

which obey the commutation relation

$$[\hat{a}, \hat{a}^{\dagger}] = 1.$$

(2.8)

As a consequence of the choice of q as coordinate the energy stored in the

capacitance represents the potential energy. The energy stored in the inductance corresponds to the kinetic energy. The same system could equally well be described using the node flux,  $\Phi$ , which is defined as the time integral

$$\Phi(t) = \int^t d\tau V(\tau), \qquad (2.9)$$

where  $V(\tau)$  is the voltage across the two lumped elements in Fig. 2.1(a). While the physical properties of the system are independent of the coordinate choice, describing using  $\Phi$  as coordinate is more convenient when the inductor is replaced with a non-linear element such as a Josephson junction (see Section 2.2). The consequence of Eq. 2.9 is that  $V(t) = \dot{\Phi}$ . The energy stored in the inductor can be written as

$$U = \frac{\Phi^2}{2L} \tag{2.10}$$

and takes the form of the potential energy. In contrast to the original coordinate choice this results in the energy stored in the capacitor corresponding to kinetic energy

$$T = \frac{1}{2}C\dot{\Phi}^2,$$

(2.11)

resulting in the Lagrangian

$$\mathcal{L} = \frac{1}{2}C\dot{\Phi}^2 - \frac{1}{2L}\Phi^2.$$

(2.12)

The momentum conjugate to the flux is given by

$$Q = \frac{\partial \mathcal{L}}{\partial \dot{\Phi}} = C \dot{\Phi}.$$

(2.13)

This definition requires that  $\hat{Q} = -\hat{q}$  and ensures the canonical commutation relations  $[\hat{q}, \hat{\Phi}] = [\hat{\Phi}, \hat{Q}] = +i\hbar$  can be maintained consistently between both coordinate systems discussed in this section. The Hamiltonian can be written in the same form as in Eq. 2.5,

$$\hat{H} = \hbar\omega \left( \hat{a}^{\dagger} \hat{a} + \frac{1}{2} \right), \qquad (2.14)$$

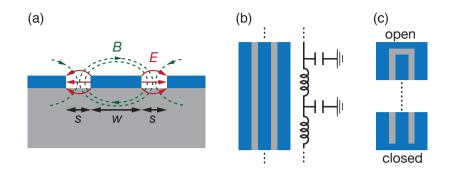

**Figure 2.2:** Coplanar waveguide geometry (a) Schematic cross section of a coplanar waveguide geometry (CPW). A CPW consists of a conductor (blue) on a substrate (grey) that forms a central conductor with width *w* and distance to the ground planes *s*. A schematic representation of the electric and magnetic field distribution of a propagating signal are added. (b) Top view schematic of a CPW structure with the corresponding circuit model. (c) Top view schematic of an open and closed end in the CPW structure. A quarter wave resonator with wavelengths  $\lambda_n = 4L'/(2n + 1)$  can be build by connecting both ends with a segment like in (b) with length *L*'.

but the raising and lowering operators take on the new form

$$\hat{a}^{\dagger} = \frac{1}{\sqrt{2\hbar\omega C}}\hat{\Phi} + i\frac{1}{\sqrt{2\hbar\omega L}}\hat{Q}$$

(2.15)

$$\hat{a} = \frac{1}{\sqrt{2\hbar\omega C}} \hat{\Phi} - i \frac{1}{\sqrt{2\hbar\omega L}} \hat{Q}.$$

(2.16)

The solutions to the Hamiltonian (Eq. 2.14) are shown in Fig. 2.1(b), where energy levels are evenly spaced and separated by  $\hbar\omega$ .

The *LC* oscillator is an important building block cQED measurements, typically used to control and read out the state of a qubit [14, 15]. It is most commonly made as a two-dimensional structure in the form of coplanar waveguides (CPW) [32].

Figure 2.2 shows the schematic of a (CPW) geometry, which is also used in this work. A CPW consists of a central conductor with width w that is separated from two ground planes by a gap of width s. The conductor sits on a substrate with permittivity  $\epsilon$ . It is usually described by its capacitance per unit length  $c(k, \epsilon)$ , its inductance per unit length  $l(k, \epsilon)$ , and its impedance  $Z(k, \epsilon)$ , where  $k = s/(s + 2w)^{\dagger}$ . The phase velocity with which a signal propagates through the CPW structure is given by  $v_p = 1/\sqrt{lc}$ . Without any boundary conditions, signals with a wide frequency range can propagate through a CPW structure. Extended CPW structures are therefore used as transmission lines. To limit the number of possible modes that can propagate through a CPW, boundary conditions must be introduced. These are usually breaks in the central conductor (open ends with  $Z = \infty$ ) and shorts to the ground plane (closed ends with  $Z \rightarrow 0$ ) as shown in Fig. 2.2(c). No current can flow at the open ends which leads to voltage anti-nodes and current nodes. The opposite configuration is true for closed ends as the voltage relative to ground must be zero. The voltage and current profiles that respect these boundary conditions are the harmonic oscillator modes of the distributed resonator, which is formed. The resonators used in this work are quarter-wave resonators, meaning they have one open and one closed end. The boundary conditions of such a quarterwave resonator with length L' result in a wavelength  $\lambda_n = 4L'/(2n+1)$ , where *n* denotes the mode number with  $n \ge 0$ . The corresponding resonance frequencies are  $\omega_n = v_p(2n+1)/(4L')$ . In many experiments a resonator can be treated as having a single mode with resonance frequency  $\omega_0$  as higher modes are far detuned from any relevant parts of the circuit.

#### 2.2 ANHARMONIC QUANTUM OSCILLATOR

Harmonic *LC* oscillators play a central role in cQED applications as discussed above but they cannot be used as a qubit while they remain completely harmonic. A qubit needs a non-linear element to enable full control over the computational subspace. If an *LC* oscillator is in the ground state, energies with  $\hbar\omega$  could excite the qubit to the first excited state but also lead to excitations to the second state as  $\omega_{01} = \omega_{12}$ . This can be avoided by using a non-linear element to change the energy potential from harmonic to (weakly) anharmonic, which has the effect that  $\omega_{01} \neq \omega_{12}$ . The non-linear element that is used to build superconducting qubits is the Josephson junction [33]. A Josephson junction (JJ) consists of two superconductors that are separated by a weak link and has a non-linear inductance *L*<sub>J</sub> associated to it. In the context of superconducting qubits, JJs most often consist of an insulator that

<sup>&</sup>lt;sup>†</sup>This is oversimplified since for many applications other important effects such as the kinetic inductance of the superconductor have to be taken into account.

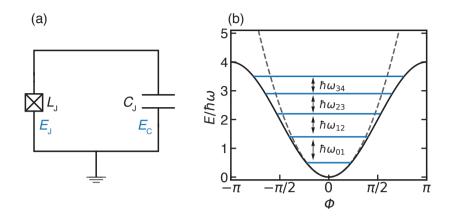

**Figure 2.3: Quantum anharmonic oscillator circuit and potential. (a)** Circuit diagram of a Josephson Junction (JJ) with Josephson inductance  $L_J$  with the associated Josephson energy  $E_J$  and capacitance of the Josephson junction  $C_J$  with the associated charging energy  $E_C$ . (b) Anharmonic potential of the JJ with sinusoidal current phase relation (solid line) and potential of the harmonic oscillator (dashed line). The energy scale is normalized to the harmonic transition energy  $\hbar \omega = \hbar / \sqrt{L_J C_J} = \sqrt{8E_J E_C}$ . Compared to the harmonic oscillator the spacing between energy levels  $|n\rangle$  is not equal and decreases with increasing state index n.

is sandwiched by two superconductors (SIS JJ) [14]. A Josephson junction is described by the two basic Josephson equations

$$I_{\rm s} = I_{\rm c} \sin\left(\phi\right) \tag{2.17}$$

$$\frac{\mathrm{d}\phi}{\mathrm{d}t} = \frac{2eV}{\hbar},\tag{2.18}$$

where  $I_s$  is the dissipationless supercurrent across the JJ,  $\phi$  is the superconducting phase difference across the superconducting leads of the JJ, and V is the voltage difference across the JJ.  $I_c$  denotes the critical current that is the largest supercurrent that the system can sustain before turning normalconducting. Equations 2.17 and 2.18 are known as DC Josephson effect and AC Josephson effect, respectively [29]. Combining both equations, the time evolution of the supercurrent can be written as

$$\frac{dI_{\rm s}}{dt} = \frac{d}{dt}I_{\rm c}\sin\left(\phi\right) = I_{\rm c}\cos\left(\phi\right)\frac{d\phi}{dt} = I_{\rm c}\cos\left(\phi\right)\frac{2eV}{\hbar}.$$

(2.19)

This in turn allows us to use the current-voltage relation of an inductor to find an expression for the Josephson inductance

$$L_{\rm J} = V \left(\frac{\mathrm{d}I_{\rm s}}{\mathrm{d}t}\right)^{-1} = \frac{\hbar}{2eI_{\rm c}\cos\left(\phi\right)}.\tag{2.20}$$

Thus, the inductance  $L_J$  of this element is non-linear and its use in conjunction with a capacitor results in an anharmonic potential, as required. Figure 2.3(a) shows the circuit diagram for a JJ, with the geometrical (and linear) capacitance  $C_J$  of the JJ taken into account. To solve the Hamiltonian, we need an expression for the energy that is associated with the current flow across the JJ. An expression can be obtained by evaluating the time integral over the power,

$$E(\phi) = \int P dt' = \int I_{s}(\phi) V(\phi) dt' = \int I_{c} \sin(\phi) \frac{\hbar}{2e} d\phi$$

$$= -\frac{\hbar I_{c}}{2e} \cos(\phi) = -E_{J} \cos(\phi) \qquad (2.21)$$

where  $E_{\rm J} = \hbar I_{\rm c}/2e$  is the characteristic Josephson energy. To compare the quantum *LC* oscillator and the anharmonic oscillator we have to map the coordinate  $\phi$  to the node flux  $\Phi$  and promote it to an operator. While  $\Phi$  is a continuous variable,  $\phi$  is a periodic coordinate in the range  $[-\pi, \pi]$ . It can be shown that  $\Phi$  is directly proportional to  $\phi$  and,

$$\hat{\phi} = \frac{\hbar}{2e} \hat{\Phi} = \frac{\Phi_0}{2\pi} \hat{\Phi}, \qquad (2.22)$$

where  $\Phi_0 = h/2e$  is the superconducting flux quantum [24]. Another aspect that has to be considered is that a JJ will always transfer one Cooper pair across the junction. The energy associated with the transfer of a single electron is given by  $E_{\rm C} = e^2/2C_{\rm J}$  [24]. The energy needed for the transfer of a Cooper pair is then given by  $E = (2e)^2/2C_{\rm J} = 4E_{\rm C}$ . Using the number operator  $\hat{n} = -\hat{q}/2e$  for the number of Cooper pairs on the capacitor, the Hamiltonian for the JJ

can be written as

$$\hat{H}_{\rm JJ} = 4E_{\rm C}\hat{n} - E_{\rm J}\cos(\hat{\phi}). \tag{2.23}$$

The  $\cos(\hat{\phi})$ -term leads to the anharmonic potential. To further emphasize the difference from the *LC* oscillator, the Hamiltonian (Eq. 2.5) can be expressed in terms of the operators  $\hat{\phi}$ ,  $\hat{n}$  as

$$\hat{H}_{\rm LC} = 4E_{\rm C}\hat{n} + \frac{E_{\rm L}}{2}\hat{\phi},$$

(2.24)

where  $E_{\rm L} = (\Phi_0/2\pi)^2/L$  is the inductive energy. This Hamiltonian only contains linear terms. Figure 2.3(b) shows the solutions to the Hamiltonian of the anharmonic oscillator (2.23), where the energy levels are not equally spaced, enabling the isolation of the two lowest energy levels. By utilizing the lowest levels one can already build a qubit system. To implement a useful qubit, we have to include circuit elements for both qubit control and qubit readout into our model, as well as take into account the environment of the qubit.

#### 2.3 Transmon

In the following chapter, we will focus on superconducting charge qubits, the *Cooper pair box* (CPB) [34, 35] and the *transmon* [23], where the transmon can be viewed as a charge-insensitive version of the CPB and is the qubit design used throughout this work.

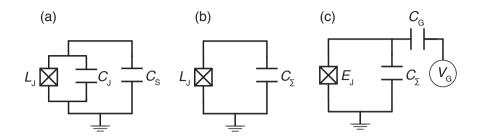

To describe the CPB we can start from the Hamiltonian and circuit diagram of a single Josephson junction and increase the complexity. In a CPB a superconducting island is connected to a superconducting reservoir via a Josephson junction. The capacitance between the island and the reservoir is described by  $C_S$ . As shown in Fig. 2.4 this can be modeled as a Josephson junction with inductance  $L_J$  in parallel with a total capacitance  $C_{\Sigma} = C_J + C_S$ . The qubit will be affected by random charges in the environment or a voltage bias might be intentionally applied to the qubit to control it. Both cases can be modeled as a voltage source that is capacitively coupled to the qubit as shown in Fig. 2.4(c). The consequences of this are twofold. First, the charging energy for this system is given by  $E_C = e^2/2C'_{\Sigma'}$ , where  $C'_{\Sigma} = C_{\Sigma} + C_G$ . Further, the

**Figure 2.4:** Cooper pair box circuit. (a) Circuit diagram of a Josephson junction in parallel with a shunt capacitor  $C_S$ . (b) Equivalent circuit to the circuit in (a), where the capacitances are combined to  $C_{\Sigma} = C_J + C_S$ . (c) A Josephson junction in parallel with a capacitor and a voltage source coupled capacitively to the circuit via  $C_G$ . This circuit diagram corresponds to the Cooper pair box discussed in the main text.

offset charge on the superconducting capacitor,

$$n_{\rm g} = -\frac{C_{\rm G} V_{\rm G}}{2e},\tag{2.25}$$

has to be considered. It is a continuous variable and represents either the effect of an externally applied electric field or some microscopic junction asymmetry that breaks the degeneracy between positive and negative charge transfer [37]. Taking this into account leads to the CPB Hamiltonian

$$\hat{H} = 4E_{\rm C} \left( \hat{n} - n_{\rm g} \right)^2 - E_{\rm J} \cos(\hat{\phi}).$$

(2.26)

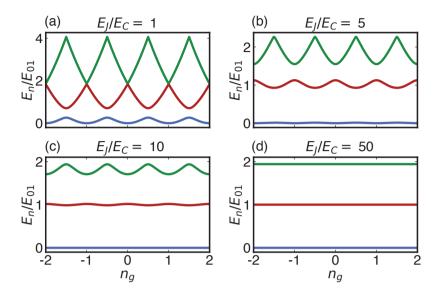

This Hamiltonian can be solved numerically in the charge basis with  $\hat{n} |n\rangle = n |n\rangle$  and  $\cos(\hat{\phi}) = 1/2 \sum (|n\rangle \langle n+1| + |n+1\rangle \langle n|)$  [37]. The solutions to the Hamiltonian are plotted in Fig. 2.5 for different ratios of  $E_J/E_C$ . These were calculated using a truncated charge space<sup>\*</sup>. In the initial experiments [35,39] the CPB was operated in the regime  $E_J \approx E_C$ , where the transition frequency  $E_{01}(n_g) = E_1(n_g) - E_0(n_g)$  between the two lowest energy levels has a strong dependence on  $n_g$ . The dependency on  $n_g$  increases for transitions involving higher levels. As a consequence, CPBs are sensitive to charge noise [35,39,40]. To increase coherence times they are typically operated at the sweet spot with

<sup>\*</sup>The code for the numerical solutions can be found in Ref. [38]

**Figure 2.5:** Numerical solutions to transmon Hamiltonian (Eq. 2.26) for four different values  $E_J/E_C$  showing the three lowest energy levels  $E_0$  (blue),  $E_1$ (red) and  $E_2$  (green) as a function of offset charge  $n_g$ . As the ratio  $E_J/E_C$  is increased from panels (a) to (d), the charge dispersion, defined as the amplitude of energy deviation as function of  $n_g$ , is substantially reduced. This figure is inspired by Ref. [23, 36]. Energies  $E_n$  are normalized with respect to  $E_{01} = E_1 - E_0$  at  $n_g = 0.25$ .

$n_{\rm g} = 1/2$ , at which point the systems is less sensitive to charge noise as the first order perturbation term  $\partial E/\partial n_{\rm g}$  is zero. Even at the sweet spot, coherence times were limited by charge noise, leading to a shift of experimental efforts in the superconducting qubit community towards charge insensitive qubits such as the transmon [14].

The transmon was first proposed in Ref. [23] and can be described as a Cooper pair box that is operated in the regime  $E_J \gg E_C$ . In this regime the charge dispersion decreases exponentially while the anharmonicity decreases algebraically. As shown in Fig. 2.5 the energy levels become -almost- independent of the offset charge  $n_g$  for large ratios of  $E_J/E_C$ . The charge insensitivity can be understood based on the description of the anharmonic oscillator laid out in Section 2.2. In this description the qubit system can be mapped onto a particle with mass *m* in the anharmonic potential. In this description,  $m \propto E_I$

and the kinetic energy corresponds to  $E_{\rm C}$ . Since  $E_{\rm J} \gg E_{\rm C}$ , the particle oscillates around  $\phi \approx 0$  and the position of the particle in phase space is localized. Due to the uncertainty principle the kinetic energy of the system, given by the charge, is no longer well defined. As a result external charge fluctuations cannot change the energy of the qubit systems and charge dispersion is reduced. Experimentally this regime is achieved by using a large shunting capacitor  $C_{\rm S} \gg C_{\rm J}$  (see Fig. 2.4).

The experimental drawback of the transmon compared to the CPB is a reduced anharmonicity  $\alpha = (E_{21} - E_{10})$  which increases leakage errors taking the qubit out of the computational subspace [14]. To calculate the anharmonicity we can expand the  $\cos(\phi)$ -term of the CPB Hamiltonian around  $\phi \approx 0$

$$E_{\rm J}\cos(\hat{\phi}) = E_{\rm J} - \frac{E_{\rm J}}{2}\hat{\phi}^2 + \frac{E_{\rm J}}{24}\hat{\phi}^4 + O(\hat{\phi}^6).$$

(2.27)

This approximation is valid in the regime  $E_J \gg E_C$ . Further, we can neglect  $n_g$  in the transmon regime as the charge dispersion is exponentially suppressed. Omitting constant terms and inserting Eq. 2.27 into Eq. 2.26 leads to the Hamiltonian

$$\begin{aligned} \hat{H} &= 4E_{\rm C}\hat{n} - E_{\rm J}\cos(\hat{\phi}) \\ &\approx 4E_{\rm C}\hat{n} + \frac{E_{\rm J}}{2}\hat{\phi}^2 - \frac{E_{\rm J}}{24}\hat{\phi}^4 = \hat{H}_0 + V'(\hat{\phi}), \end{aligned}$$

(2.28)

where  $\hat{H}_0 = 4E_C\hat{n} + \frac{E_J}{2}\hat{\phi}^2$  takes the form of the Hamiltonian of the harmonic oscillator. The corresponding plasma frequency is given by  $\hbar\omega_r = 1/\sqrt{L_JC_{\Sigma}} = \sqrt{8E_JE_C}$ , where  $C_{\Sigma}$  is the sum of all capacitances in the system [see Fig. 2.6(c)]. The term  $V'(\hat{\phi}) = E_J\hat{\phi}^4/24$  can be treated as perturbation to  $\hat{H}_0$ , which enables us to calculate the anharmonicity. In order to do so we can express the operators  $\hat{n}$  and  $\hat{\phi}$  in terms of ladder operators of the Harmonic oscillator (see Section 2.1).

$$\hat{a}^{\dagger} = \sqrt{\frac{E_{\rm J}}{2\hbar\omega}}\hat{\phi} + 2i\sqrt{\frac{E_{\rm C}}{\hbar\omega}}$$

(2.29)

$$\hat{a} = \sqrt{\frac{E_{\rm J}}{2\hbar\omega}}\hat{\phi} - 2i\sqrt{\frac{E_{\rm C}}{\hbar\omega}}.$$

(2.30)

This, in turn, enables us to express  $\hat{\phi}$  and  $\hat{n}$  in terms of ladder operators and relevant energy scales as

$$\hat{\phi} = \left(\frac{2E_{\rm C}}{E_{\rm J}}\right)^{1/4} \left(\hat{a} + \hat{a}^{\dagger}\right) \tag{2.31}$$

$$\hat{n} = \left(\frac{E_{\rm J}}{2E_{\rm C}}\right)^{1/4} \left(\hat{a} - \hat{a}^{\dagger}\right).$$

(2.32)

Inserting this back into the Eq. 2.28 yields

$$\hat{H}_0 = \hbar\omega \left( \hat{a}^\dagger \hat{a} + \frac{1}{2} \right) \tag{2.33}$$

$$V'(\hat{\phi}) = -\frac{E_{\rm J}}{12} \left( \hat{a} + \hat{a}^{\dagger} \right)^4.$$

(2.34)

Applying the rotating wave approximation, by neglecting all terms with an uneven number of raising and lowering operators, the perturbation can be written as

$$V'(\hat{\phi}) = -\frac{E_{\rm J}}{12} \left( \hat{a} + \hat{a}^{\dagger} \right)^4 = -\frac{E_{\rm C}}{2} \left( \hat{a}^{\dagger} \hat{a}^{\dagger} \hat{a} \hat{a} + 2\hat{a}^{\dagger} \hat{a} \right).$$

(2.35)

This leads to corrections for the first three energy levels relative to the harmonic oscillator solutions

$$\langle 0 | V'(\hat{\phi}) | 0 \rangle = 0 \tag{2.36}$$

$$\langle 1|V'(\hat{\phi})|1\rangle = -E_{\rm C} \tag{2.37}$$

$$\langle 2 | V'(\hat{\phi}) | 2 \rangle = -3E_{\rm C},$$

(2.38)

leading to the transition energies

$$E_{10} \approx E_1 - E_0 = \sqrt{8E_{\rm J}E_{\rm C}} - E_{\rm C} \tag{2.39}$$

$$E_{21} \approx E_2 - E_1 = \sqrt{8E_J E_C} - 2E_C,$$

(2.40)

and an anharmonicity

$$\alpha = E_{21} - E_{10} \approx -E_{\rm C}.\tag{2.41}$$

#### 2.4 Qubit readout

In the previous sections we described the transmon qubit and introduced an element of control in the form of an external voltage which can be used to set the offset charge. However, any useful quantum algorithm requires a way to manipulate and effectively read out the qubit state. Additionally, many proposed quantum algorithms rely on active error correction, requiring quantum non-demolition measurements that preserve the qubit state [24]. As we will discuss in this section, both qubit manipulation and qubit readout can be performed via an *LC* oscillator that is coupled to the qubit.

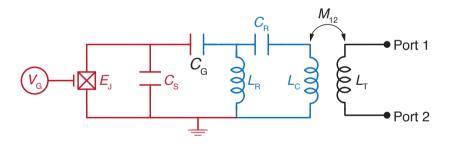

Figure 2.6 shows the circuit diagram of a circuit that is typically used to measure a voltage-controlled transmon qubit. Here, the transition frequency  $\omega_{01}$  - henceforth only referred to as qubit frequency  $\omega_{q}$ - can be controlled by changing  $E_J$  via the gate voltage  $V_G$ . The qubit is coupled to a distributed *LC* resonator with a total capacitance  $C_r$ , total inductance  $L_r$ , and resonance frequency  $\omega_r = (2\pi)/\sqrt{L_rC_r}$  (see Fig. 2.6). The resonance frequency is chosen such that only the lowest mode of the resonator is close to the qubit frequency. Higher resonator modes can be neglected. The resonator is coupled inductively to a transmission line. The system can be described by the Hamiltonian

**Figure 2.6: Coupled transmon circuit.** Circuit diagram representing a voltage-tunable transmon (red) that is capacitively coupled to a readout resonator with inductance  $L_R$  and capacitance  $C_R$  (blue). The qubit and and resonator are coupled by capacitance  $C_G$ . The readout resonator with coupling inductance  $L_C$  is inductively coupled to a transmission line with inductance  $L_T$  (black) by the mutual inductance  $M_{12}$ . The qubit frequency can be controlled via a gate voltage  $V_G$  that is applied to the Josephson junction to modulate  $E_J$ .

$$\hat{H} = 4E_{\rm C}\hat{n} - E_{\rm J}\cos(\hat{\phi}) + \hbar\omega_{\rm r}\hat{a}^{\dagger}\hat{a} + 2\beta eV_{\rm rms}^{0}\hat{n}(\hat{a} + \hat{a}^{\dagger}), \qquad (2.42)$$

where  $\beta = C_G/C_{\Sigma}$  and  $V_{\rm rms}^0 = \sqrt{\hbar\omega_r/(2C_r)}$  is the root mean square voltage of the resonator at the point where it couples to the shunting capacitor [23]. Here, the first two terms correspond to the uncoupled CPB Hamiltonian (Eq. 2.28). The third term represent the lowest mode of the resonator. The fourth term describes the resonator-qubit coupling. Rewriting the Hamiltonian in the basis of the uncoupled transmon states  $|i\rangle$ , one obtains the generalized Jaynes-Cummings Hamiltonian

$$\hat{H} = \hbar \omega_{\rm r} \hat{a}^{\dagger} \hat{a} + \hbar \sum_{i} \omega_{\rm i} |i\rangle \langle i| + \hbar \sum_{i,j} g_{\rm ij} |i\rangle \langle j| \left(\hat{a} + \hat{a}^{\dagger}\right), \qquad (2.43)$$

where the coupling strength  $g_{ij}$  between is levels *i* and *j* are given by the expression

$$\hbar g_{ij} = 2\beta e V_{\rm rms}^0 \langle i | \, \hat{n} \, | j \rangle \,. \tag{2.44}$$

Equation 2.43 can be significantly simplified when analyzing the matrix elements and using the rotating wave approximation. The only matrix element with a significant contribution is the element  $\langle i + 1 | \hat{n} | i \rangle$  as all other matrix elements asymptotically approach zero in the transmon limit  $E_J/E_C \rightarrow 0$ . Employing the rotating wave approximation, terms that do not conserve the number of excitations in the system can be eliminated. This leads to the effective generalized Jaynes-Cummings Hamiltonian

$$\hat{H} = \hbar \omega_{\rm r} \hat{a}^{\dagger} \hat{a} + \hbar \sum_{i} \omega_{\rm i} |i\rangle \langle i| + \hbar \sum_{i} g_{\rm i,i+1} \left( |i\rangle \langle i+1| \hat{a}^{\dagger} + |i+1\rangle \langle i| \hat{a} \right). \quad (2.45)$$

Simplifying further, the qubit system can be approximated as an effective twolevel system. Rewriting the Hamiltionian in terms of the qubit frequency  $\omega_q$ , the spin Pauli operators  $\hat{\sigma}_z$  and the spin ladder operators  $\hat{\sigma}_{\pm} = \hat{\sigma}_x \pm i\hat{\sigma}_y$ , leads to the original Jaynes-Cummings Hamiltonian [41,42]

$$\hat{H} = \hbar \omega_{\rm r} \hat{a}^{\dagger} \hat{a} + \frac{\hbar \omega_{\rm q}}{2} \hat{\sigma}_{\rm z} + \hbar g_{01} \left( \hat{a}^{\dagger} \hat{\sigma}_{-} + \hat{\sigma}_{+} \hat{a} \right).$$

(2.46)

The Jaynes-Cummings Hamiltonian has two distinct regimes. In the resonant regime,  $\omega_r \approx \omega_q$  the qubit and resonator hybridize into new states that are

superpositions of the qubit excitation states and the resonator photon states. These new states are split by the vacuum Rabi splitting  $2\hbar g_{01}$ . In order to achieve quantum non-demolition (QND), the qubit is operated in the dispersive regime that allows for quantum non-demolition measurements [42]. In this dispersive limit the detuning between qubit and resonator  $\Delta_0$  is large compared to the coupling ( $|\Delta_0| = |\omega_r - \omega_q| \gg g$ ). Expanding around  $g/\Delta_0$  and restricting the Hilbert space to the lowest two levels leads to the effective Hamiltonian

$$\hat{H}_{\text{eff}} = \frac{\hbar\omega'_{\text{q}}}{2}\hat{\sigma}_{\text{z}} + \hbar\left(\omega'_{\text{r}} + \chi\hat{\sigma}_{\text{z}}\right), \qquad (2.47)$$

where  $\omega'_q = \omega_q + \chi$  and  $\omega'_r = \omega_r - \chi_{12}/2$  are the renormalized qubit and resonator frequencies, respectively [23]. The harmonic frequency shifts are defined as

$$\chi_{ij} = \frac{g_{ij}^2}{\omega_0 - \omega_r} \tag{2.48}$$

$$\chi = \chi_{01} - \frac{\chi_{12}}{2}.$$

(2.49)

The key feature in this regime is that the resonator frequency shifts by  $\pm \chi$  depending on the qubit state, meaning the qubit state can be inferred from a resonator measurement. The other crucial aspect here is that the qubit remains in the measured state after readout. Therefore a resonator measurement constitutes a quantum non-demolition measurement of the qubit. Using  $\omega_{12} = \omega_{01} + \alpha/\hbar$  and  $g_{12} = \sqrt{2}g_{01}$ , the frequency shift can be written as

$$\chi = \chi_{01} - \frac{\chi_{12}}{2} = \frac{g_{01}^2}{\Delta_0} - \frac{g_{01}^2}{\Delta_0 + \alpha/\hbar}.$$

(2.50)

As highlighted by Eq. 2.50 a sufficiently large anharmonicity is needed for a resonator shift that is large enough to be detected. Ideally, a large coupling strength  $g_{01}$  would be chosen in most experiments if it would not cause adverse effects. For instance, the spontaneous decay rate of the qubit is modified by the decay rate of the resonator  $\kappa$ , which is known as the Purcell effect [43,44].

The Purcell decay rate is given by

$$\gamma_{\kappa} = \kappa \frac{g_{01}^2}{\Delta_0^2}.$$

(2.51)

Without the aid of measures such as the use of a Purcell filter to mitigate losses [45], we choose a trade off that enables a large enough resonator shift while keeping the Purcell decay rate below the qubit state decay rate.

#### 2.5 QUBIT MANIPULATION

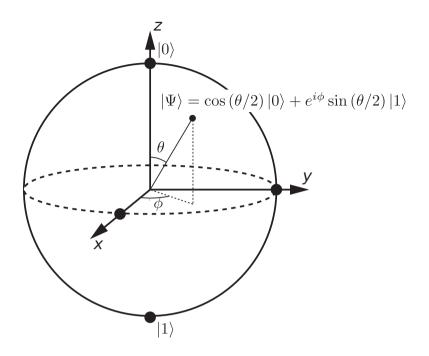

In the previous section we described the qubit as a quantum mechanical twolevel system. In order to realize the potential of such a system for quantum computation it is fundamentally important to be able to control it, starting from the ability to prepare a qubit in any linear combination of the ground state  $|0\rangle$  and the first excited state  $|1\rangle$ . As illustrated in Fig. 2.7, any state can be visualized as a vector on the Bloch sphere  $|\Psi\rangle = \cos(\theta/2) |0\rangle + e^{i\phi} \sin(\theta/2) |1\rangle$ .

Any single qubit operation can be visualized as a series of rotations of the qubit state around the *x* and *y* axes. In our experiment these rotations are generated by microwave tones that are coupled to the qubit, either through a drive line or the readout resonator. The Hamiltonian in Eq. 2.47 can be expanded to account for an external time-dependent drive of the kind  $V_d(t) = v_R \cos(\omega_d t) + v_I \sin(\omega_d t)$ , where  $v_R$  and  $v_I$  denote the in-phase and out-of-phase part of the drive signal, respectively, and  $\omega_d$  is the drive frequency. In the rotating frame of the drive the Hamiltonian can be written as

$$\hat{H} = \hbar \left( \Delta_{\rm r} + \chi \hat{\sigma}_{\rm z} \right) \hat{a}^{\dagger} \hat{a} + \frac{\hbar \Delta_{\rm q} \hat{\sigma}_{\rm z}}{2} + \frac{\hbar}{2} \left( \Omega_{\rm R}(t) \hat{\sigma}_{\rm x} + \Omega_{\rm I}(t) \hat{\sigma}_{\rm y} \right), \qquad (2.52)$$

where  $\Delta_r = \omega_r - \omega_d$ ,  $\Delta_q = \omega_{01} - \omega_d$  and  $\Omega_{R,I} = 2e\beta \langle 0||\hat{n}|1\rangle v_{R,I}$ . In this description  $\Omega_{R,I}$  are Rabi frequencies, the frequencies of the driven system with which the state rotates around the *x*-axis (with frequency  $\Omega_R$ ) and *y*-axis (with frequency  $\Omega_I$ ). Equation 2.52 describes a superconducting transmon, which is coupled to a readout resonator and can be manipulated with an external drive, enabling full qubit control and readout. This Hamiltonian describes the qubit devices that are the focus of this work and discussed in Chapters 5 and 7. The experimental implementation of Eq. 2.52 will be

**Figure 2.7: Bloch sphere** representation of a qubit state  $|\Psi\rangle$  as a unit vector anywhere on the surface of the sphere. The state  $|\Psi\rangle$  can be described using the angles  $\theta$  and  $\phi$ .

discussed in Section 4.7.

# 2.6 Semiconductor-based superconducting qubits

In the previous sections we assumed two properties of the Josephson junction (JJ). Firstly, that the critical current and therefore  $E_J$  is tunable with an external voltage and secondly, that the current-phase relationship (CPR) of the junction is sinusoidal (Eq. 2.17). However, most state-of-the art transmons are not gate-tunable. The JJs in these transmons are commonly realized by an material stack that is made out of Al/Al<sub>2</sub>O<sub>3</sub>/Al, where the insulating Al<sub>2</sub>O<sub>3</sub> layer is only a few nanometers thick [14]. Two junctions are built in parallel to form a superconducting quantum interference device (SQUID [46]. The critical current  $I_C$  (hence  $E_J$ ) of the SQUID is controlled via an magnetic flux that is

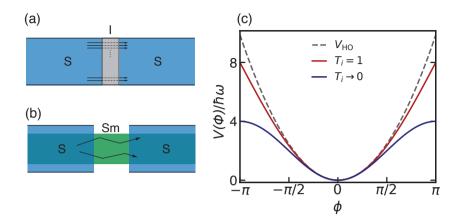

**Figure 2.8:** Short junction potential. Comparison of an (a) SIS and (b) SSmS Josephson junction. The SIS junction has many low transmitting channels while the SSmS junction has few highly transmitting channels. (c) Short junction Josephson potential  $V(\phi)$  (Eq. 2.53) in the limits  $T_i \rightarrow 0$  (blue) and  $T_i = 1$  (red). For comparison the potential of the harmonic oscillator  $V_{\text{HO}}$  is plotted as a dashed line. The potentials are normalized to the harmonic resonance frequency  $\omega$  and offset to all equal 0 at  $\phi = 0$ .

threaded through the SQUID loop.

Gate-tunable junctions and qubits have been realized with superconductorsemiconductor-superconductor (SSmS) junctions [21, 22], where  $I_C$  can be tuned by tuning the semiconductor segment of the junction. The CPR of a SSmS junction is not sinusoidal<sup>†</sup>.

Figures 2.8(a) and (b) show a schematic representation of an SIS and SSmS junction. In the case of an SIS junction, the junction has many low-transmitting channels and the current-phase relationship is well described by Eq. 2.17. In contrast, SSmS junctions have a few highly transmitting channels [47]. The charge is transferred via so-called Andreev bound states that will be discussed in more detail in Section 3.3. In the ballistic limit where the superconducting coherence length is much larger than the junction length, the Andreev bound

<sup>&</sup>lt;sup>+</sup>A sinusoidal CPR can be retrieved in the tunnel limit where the semiconductor is effectively depleted but otherwise not present (see Eq. 2.57).

states lead to a Josephson potential of the form

$$V(\hat{\phi}) = -\Delta \sum_{i} \sqrt{1 - T_{i} \sin^{2}(\hat{\phi}/2)},$$

(2.53)

where  $\Delta$  is the superconducting gap and  $T_i$  is the transmission probability of the  $i_{th}$  channel [48]. In the case  $T_i \rightarrow 0$  the potential  $V(\hat{\phi})$  approaches a  $\cos(\phi)$ -potential. This is the potential used previously to describe the anharmonic oscillator in Section 2.2. It is illustrated in Fig. 2.3(b) and described by Eq. 2.21. For  $T_i = 1$  the potential is still weakly anharmonic but more closely resembles the potential of a harmonic oscillator [see Fig. 2.1(b)]. A comparison of all three potentials is shown in Figure 2.8(c). As a consequence the anharmonicity depends on the transmission of the single channels. To calculate the anharmonicity we can follow the procedure described in Section 2.3 and expand  $V(\hat{\phi})$  to the fourth order in  $\hat{\phi}$ . A more detailed derivation can be found in Ref. [36]. For  $E_{\rm I} \gg E_{\rm C}$  and  $\phi \approx 0$  the potential can be written as

$$V(\hat{\phi}) = E'_{\rm J} \frac{\hat{\phi}^2}{2} - E'_{\rm J} \left( 1 - \frac{3}{4} \frac{\sum T_i^2}{\sum T_i} \right) \frac{\hat{\phi}^4}{24} + O(\hat{\phi}^6)$$

(2.54)

with

$$E'_{\rm J} = \frac{\Delta}{4} \sum T_{\rm i}.$$

(2.55)

With the definition of  $E'_{\rm J}$  the harmonic part of the potential can be written as  $V_0(\hat{\phi}) = \frac{E'_{\rm J}}{2}\hat{\phi}^2$ . Treating the rest of the potential as perturbation

$$V_0'(\hat{\phi}) = -E_J'\left(1 - \frac{3}{4} \frac{\sum T_i^2}{\sum T_i}\right) \frac{\hat{\phi}^4}{24}$$

(2.56)

and applying the rotating wave approximation, the transmission dependent anharmonicity can expressed as

$$E_{12} - E_{01} = \alpha \approx -E_C \left( 1 - \frac{3}{4} \frac{\sum T_i^2}{\sum T_i} \right)$$

(2.57)

as shown in Ref. [36]. This result demonstrates that the anharmonicity can be

reduced to  $\alpha = -E_C/4$  in the limit of T = 1. In the tunnel limit  $T_i \rightarrow 0$  the result  $\alpha = -E_C$  of a transmon with an SIS junction is recovered.

In this chapter we discussed the *LC* oscillator, the SIS Josephson junction, and the transmon in the framework of cQED. Additionally, we described the coupled system of a transmon and an *LC* oscillator for qubit manipulation and readout. This formulation is the basis of quantum computing with superconducting qubits and necessary to understand the qubit characterization in Chapter 5 and 7. Further, we have discussed the difference between the standard insulator-based transmon and the gate-voltage tunable semiconductor-based transmon, often referred to as a gatemon [21,22]. Here, the qubit system was described using macroscopic degrees of freedom, such as inductance, capacitance and critical current. In Chapter 3 we will give a microscopic description of the processes that appear at the interface between semiconductor and semiconductor, namely Andreev reflections, and the Josephson effect in terms of Andreev bound states.

# 3 Superconductor-Semiconductor Hybrid Systems

In the previous chapter, we have described superconductor-semiconductorsuperconductor Josephson junction as a building block for a transmon in the framework of cQED. In this chapter, we will focus on the microscopic description of the electric properties of superconductor-semiconductor hybrid systems in terms of Andreev reflections. These are introduced in Section 3.1. Section 3.2 gives a brief summary of the Blonder-Tinkham-Klapwijk (BTK) formalism for the charge transport across an NS interface and the proximity effect. This is followed by the description of an SNS junction in terms of Andreev reflections and within the resistively shunted junction model in Sections 3.3 and 3.4, respectively. Section 3.5 discusses the  $I_CR_N$  product for different junction limits. Lastly, Section 6.6 presents the concept of multiple Andreev reflections. These concepts are necessary to understand the measurements presented in Chapter 6.

#### 3.1 ANDREEV REFLECTIONS

To understand the properties of a semiconductor in the proximity of a superconductor, it is crucial to understand the processes at the material interface.

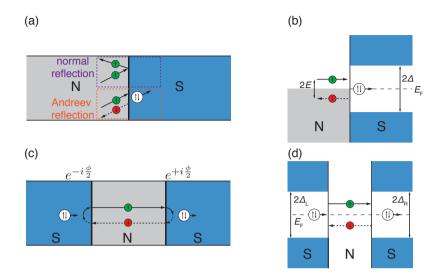

**Figure 3.1:** Andreev reflections in real and energy space. (a) Real space schematic of a normal reflection and Andreev reflections at an NS interface. In this example an electron (green) with spin up ( $\uparrow$ ) is Andreev reflected, meaning being retroreflected as a hole (red) with spin down ( $\downarrow$ ) and retracing the trajectory of the incident electron. As result a Cooper pair in the superconductor is created. (b) Energy schematic of Andreev reflections. (c) Real space schematic representation of an Andreev bound state in an SNS junction with phase difference  $\phi$  between the superconducting regions. (d) Energy space representation of an Andreev bound state in an SNS junction.

When the semiconductor, which is modeled as a normal conductor, and superconductor are in contact, the Fermi energies  $E_F$  of both materials are aligned. While electron states in the normal conductor (N) with energies  $E \le E_F$  are occupied, no single particle states with  $E_F - \Delta < E < E_F + \Delta$  exist in the superconductor (S), where  $\Delta$  is the superconducting gap.

Figure 3.1(a) shows the two ways an electron can reflect at an NS interface for  $E < \Delta$ . First, it could normal reflect, where the electron is reflected back into the normal conductor. As we will see in Section 3.2.1, normal reflections only occur if the interface is imperfect or the incident electron has an energy  $E > \Delta$ . In case of a perfect interface and  $E < \Delta$ , *Andreev reflections* will occur [49], meaning the incident electron with momentum  $\vec{k}$  and spin up ( $\uparrow$ ) propagates into the superconductor and the normal conductor donates an additional electron with  $\vec{k} \downarrow$  and energy -E. As a results. the superconductor accepts a Cooper pair ( $\vec{k} \uparrow, -\vec{k} \downarrow$ ) with energy  $E_F$ . This process can equally well be represented as the incident electron being retroreflected as a hole with momentum  $-\vec{k}$  [see Figs. 3.1(a)-(b)].

The qualitative description above can be generalized for imperfect interfaces to describe electrical transport across an NS interface quantitatively. Interfaces will always be degraded due to sample processing or imperfect materials. Further, the Fermi velocity mismatch between semiconductor and superconductor is taken into account.

## 3.2 TRANSPORT ACROSS NS INTERFACE

#### 3.2.1 The Blonder-Tinkham-Klapwijk formalism

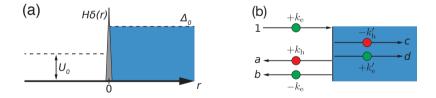

The Blonder-Tinkham-Klapwijk formalism describes the electrical transport across an imperfect NS interface [50]. The system is modeled with the potential shown in Fig. 3.2(a), where the interface between semiconductor and superconductor is described with the potential  $H\delta(r)$ , where  $\delta(r)$  is the Dirac delta function. Instead of H, the dimensionless unit

$$Z = H \frac{m_{\rm e}}{\hbar v_{\rm F}},\tag{3.1}$$

is typically used to describe the interface, where  $v_F$  denotes the Fermi velocity and  $m_e$  is the electron mass. This *Z*-parameter is often used synonymously with the interface quality, where Z = 0 correspond to a perfect interface with-

**Figure 3.2:** Schematic NS interface in the BTK model. (a) The potential between normal conductor (white) and superconductor (blue) is modeled using the conduction band offset  $U_0$ , the pairing potential  $\Delta_0$ , and a Dirac  $\delta$ -function with height *H* at the interface. (b) Definition of the plane-wave coefficients used in the BTK analysis.

out barrier. Additionally, different charge carrier densities in both materials lead to a difference in  $E_F$ , which lifts the conduction band of the semiconductor relative to the superconductor by  $U_0$ . The Fermi velocity mismatch is modeled by a potential step across the interface, leading to the potential

$$U(r) = U_0 \theta(-r) + H\delta(r), \qquad (3.2)$$

where  $\theta(r)$  is the Heaviside step function. Further, the pair potential increases in a step-like manner  $\Delta(r) = \Delta_0 e^{-i\phi} \theta(r)$  as shown in Fig. 3.2(a). In order to calculate the particle transfer across the interface, the Bogoliubov-de Gennes equations are utilized [29]. The corresponding Hamiltonian is

$$H(r) = \frac{\hbar^2}{2m^*} \nabla_{\rm r}^2 - \mu + U(r), \qquad (3.3)$$

where  $m^*$  corresponds to the effective mass of the electrons in the semiconductor and  $\mu$  denotes the chemical potential. Fig. 3.2(b) illustrates the possible outcomes of a scattering event at the interface. An incident electron at the interface can be scattered in four different ways: as a reflected electron (normal scattering), as a retroreflected hole (Andreev reflection), be transmitted as a quasi-electron or be transmitted as a quasi-hole. Using the plane-wave ansatz this can be expressed by three wave functions

$$\Psi_{\text{incoming}} = \begin{pmatrix} 1\\ 0 \end{pmatrix} e^{ik_{e}r}$$

(3.4)